Datafloq enables anyone to contribute articles, but we value high-quality content. This means that we do not accept SEO link building content, spammy articles, clickbait, articles written by bots and especially not misinformation. Therefore, we have developed an AI, built using multiple built open-source and proprietary tools to instantly define whether an article is written by a human or a bot and determine the level of bias, objectivity, whether it is fact-based or not, sentiment and overall quality.

Articles published on Datafloq need to have a minimum AI score of 60% and we provide this graph to give more detailed information on how we rate this article. Please note that this is a work in progress and if you have any suggestions, feel free to contact us.

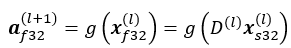

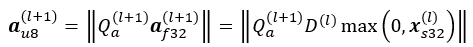

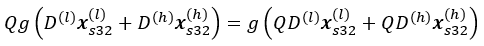

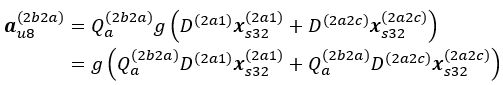

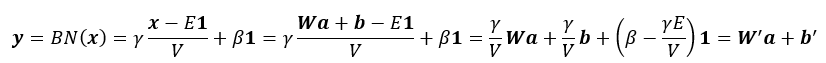

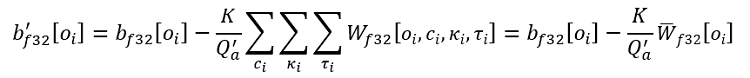

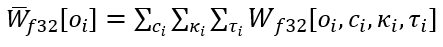

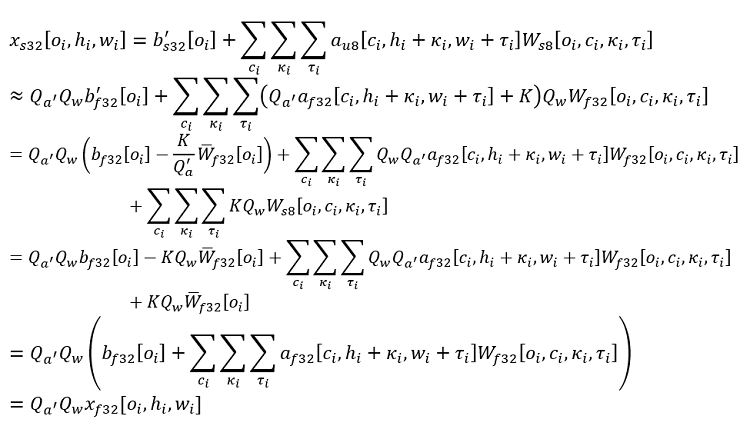

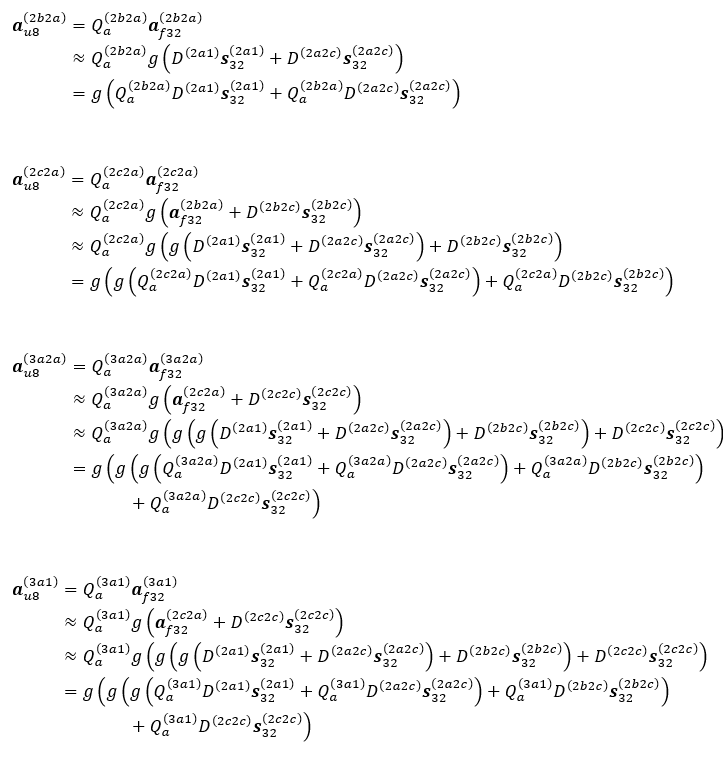

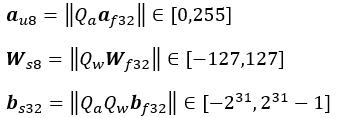

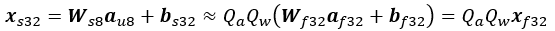

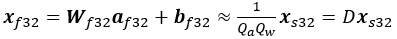

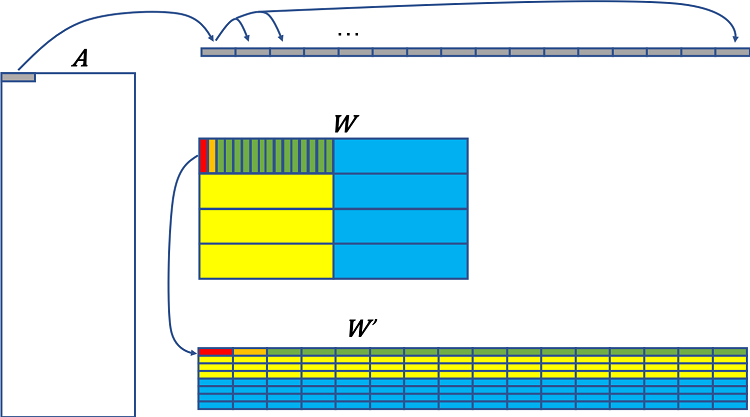

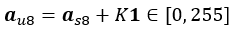

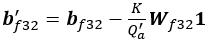

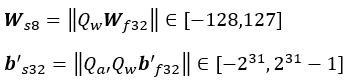

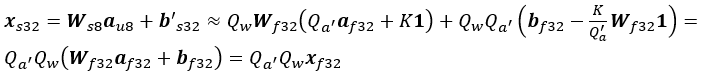

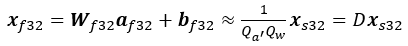

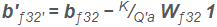

For a convolution layer the product W32 1 is generalized to equal the sum over all the values of W32 along all dimensions except the dimension shared with b32. See Appendix A for details.

For a convolution layer the product W32 1 is generalized to equal the sum over all the values of W32 along all dimensions except the dimension shared with b32. See Appendix A for details.